# Four Probe, *In Situ* Electrical Characterization of Dopant Structures in Silicon

Craig Polley

# THE UNIVERSITY OF NEW SOUTH WALES

A thesis submitted in fulfilment of the requirements for the degree **Doctor of Philosophy**

August 2012

Minor corrections August 2016

## **Abstract**

In this thesis we demonstrate the *in situ* electrical characterization of planar, high concentration phosphorus layers in silicon close to the silicon-vacuum interface. To achieve this we have used an ultra-high vacuum four-probe scanning tunneling microscope (STM) in combination with a gaseous molecular dopant precursor ( $PH_3$ ) and a silicon sublimation source for epitaxial encapsulation.

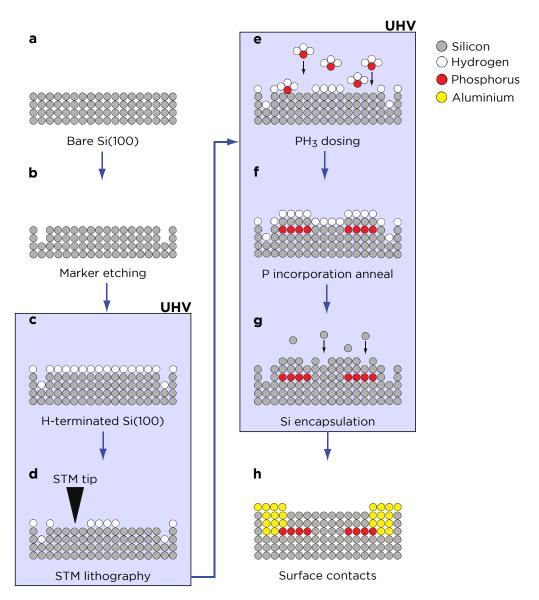

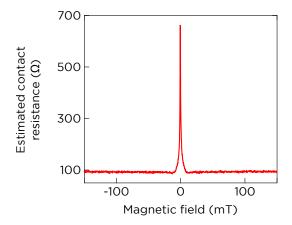

Initially we investigate and improve *ex situ* Ohmic contact formation to highly phosphorus doped silicon using nickel silicide rather than aluminium. We demonstrate improved reliability, depth control and the elimination of superconducting artifacts.

We develop a comprehensive understanding of how an *in situ* four-probe scanning tunneling microscope system can be applied for the measurement of electrical resistivity, both for bulk doped substrates and near-surface  $\delta$ -doping profiles. Through extensive measurements we show that the sheet resistance of  $\delta$ -doping layers can be reliably and unambiguously characterized, even at room temperature using conductive substrates.

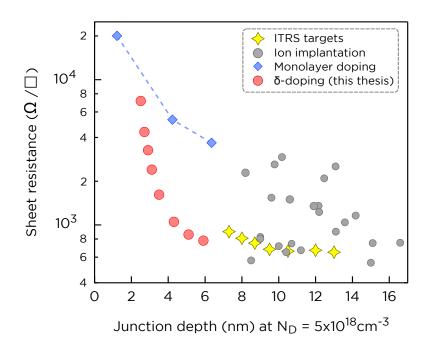

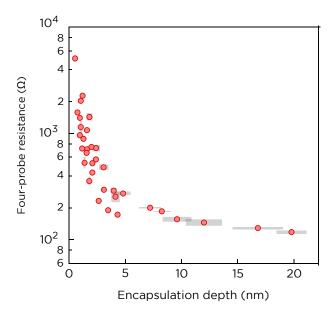

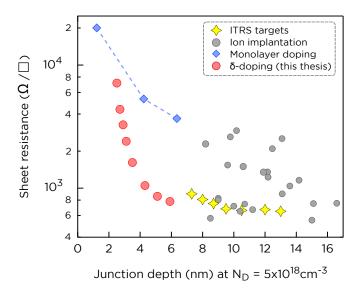

Building on this, we then investigate the technologically relevant topic of how the resistivity of these degenerate 2D doping layers evolves as a function of their depth from the silicon-vacuum interface. We observe Ohmic conduction at depths as low as 0.5 nm, with a resistivity which sharply decreases from  $\approx\!24~\mathrm{k}\Omega/\Box$  until saturating at  $\approx\!550~\Omega/\Box$  for depths beyond approximately 20 nm. Importantly, the sheet resistances we obtain at the depths we obtain them surpass all currently projected requirements from the International Technology Roadmap for Semiconductors (ITRS) for ultra-shallow junctions. We are able to explain the depth dependence with a conductivity model incorporating a finite segregation length of the grown layer combined with surface scattering.

Finally we extend this four-probe work towards the measurement of STM patterned dopant regions close to the interface. We obtain preliminary one-, two- and four-terminal resistance measurements on micrometer scale lithographically defined dopant patches. We highlight the challenges in such an endeavour, and show that probe-to-sample conductance measurements provide an unambiguous test of positioning accuracy.

Combined, using a four-probe STM we have built a solid experimental grounding for the understanding and further exploration of near-surface dopant structures in silicon.

# **Contents**

| 1 | Intr | oductio  | on Control of the Con | 1  |

|---|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | A ni | ickel si | licide contacting scheme for $\delta$ -doped silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5  |

|   | 2.1  | Introd   | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

|   |      | 2.1.1    | An overview of STM device fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7  |

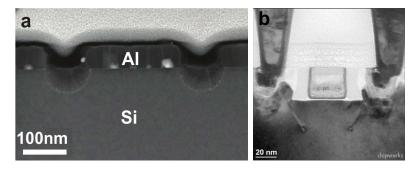

|   |      | 2.1.2    | Limitations in the existing contacting process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

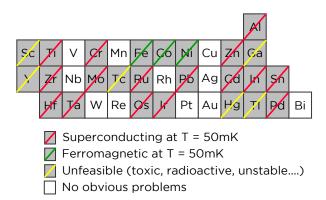

|   | 2.2  | Choos    | sing an optimal Ohmic contact metallization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 |

|   |      | 2.2.1    | Overview of a generic metal-semiconductor contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13 |

|   |      | 2.2.2    | Requirements and limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 |

|   |      | 2.2.3    | Candidate schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |

|   |      | 2.2.4    | Why nickel silicide?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

|   | 2.3  | Devel    | oping a nickel silicide contact recipe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

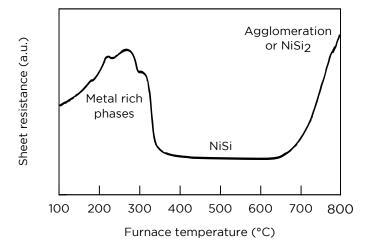

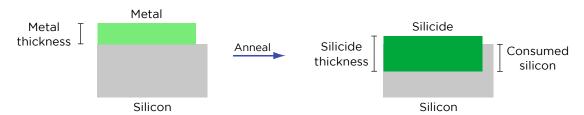

|   |      | 2.3.1    | Making nickel silicide: lessons from the literature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

|   |      | 2.3.2    | Developing a nickel silicide process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 |

|   |      | 2.3.3    | Final NiSi fabrication recipe with example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29 |

|   | 2.4  | Comp     | arative electrical characterization study of Al and NiSi contacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

|   |      | 2.4.1    | Methodology and initial characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34 |

|   |      | 2.4.2    | Extracting the Ohmic contact resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36 |

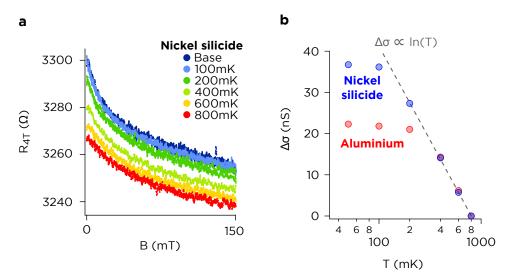

|   |      | 2.4.3    | The impact of metallization on electrical transport properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

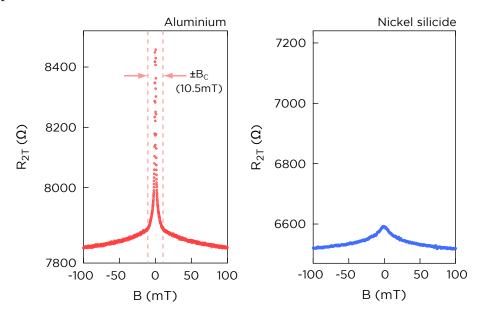

|   |      | 2.4.4    | Understanding and eliminating superconductivity artifacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40 |

|   |      | 2.4.5    | Comparing the magnitude of hysteresis in magnetotransport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43 |

|   | 2.5  | Concl    | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47 |

| 3 | Fou  | r point  | probe resistivity measurements of $\delta$ -doped silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49 |

|   | 3.1  | Four-p   | point probe measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51 |

|   |      | 3.1.1    | Extracting resistivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52 |

|   |      | 3.1.2    | Sources of error and other considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55 |

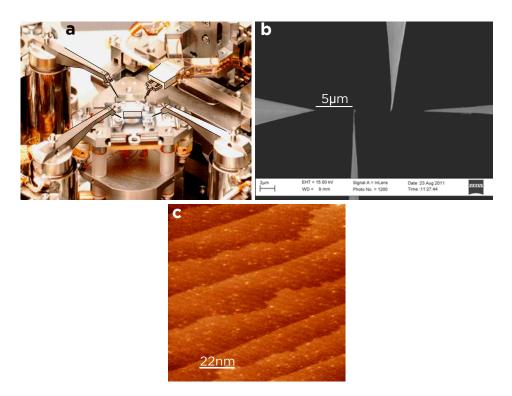

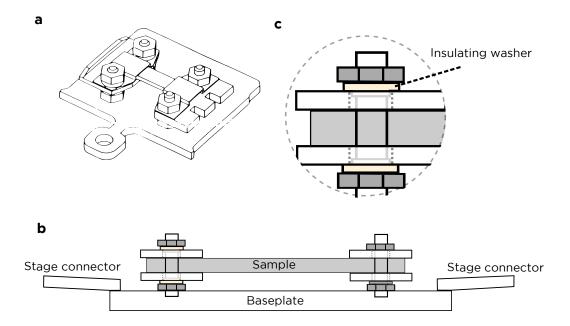

|   |      | 3.1.3    | The Omicron Nanoprobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59 |

|   | 3.2  | Chara    | cterizing the substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61 |

|   |      | 3.2.1    | Experimental method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62 |

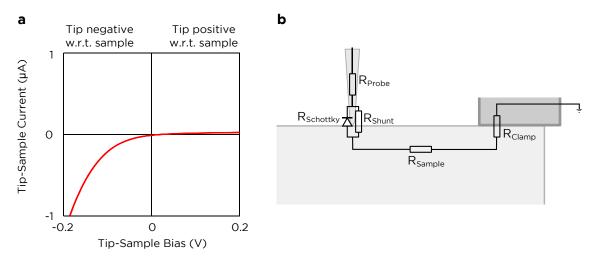

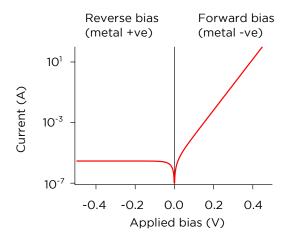

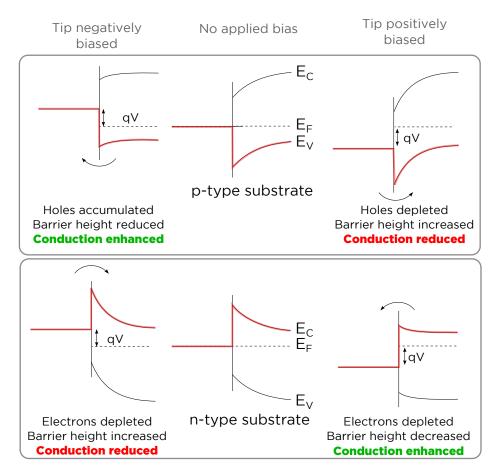

|   |      | 322      | Tin-to-sample I-V characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63 |

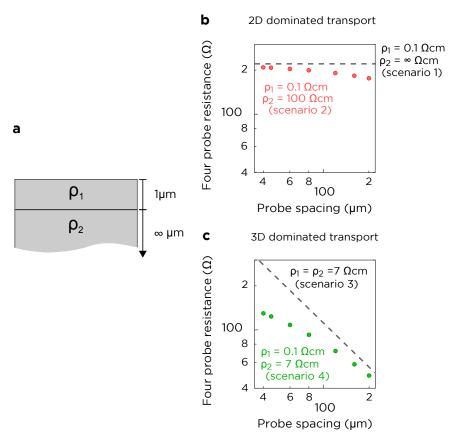

|   |     | 3.2.3  | Probe spacing dependent four-terminal measurements                          | 70  |

|---|-----|--------|-----------------------------------------------------------------------------|-----|

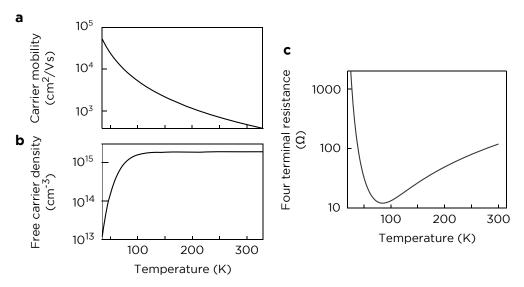

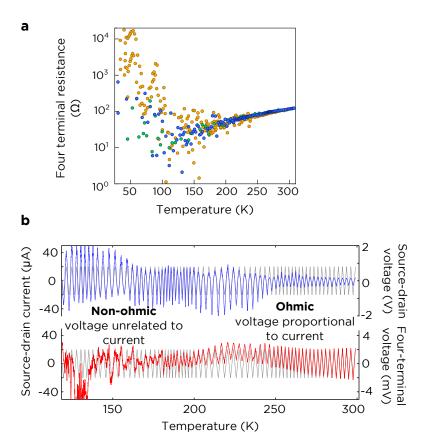

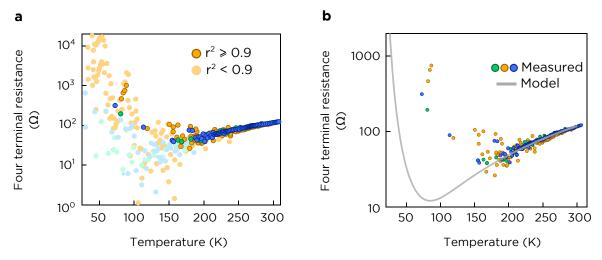

|   |     | 3.2.4  | Temperature dependence of resistivity                                       | 75  |

|   | 3.3 | Electr | ical active delta-layers                                                    | 83  |

|   |     | 3.3.1  | Experimental method                                                         | 83  |

|   |     | 3.3.2  | I-V characteristics                                                         | 84  |

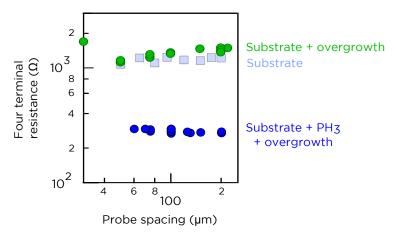

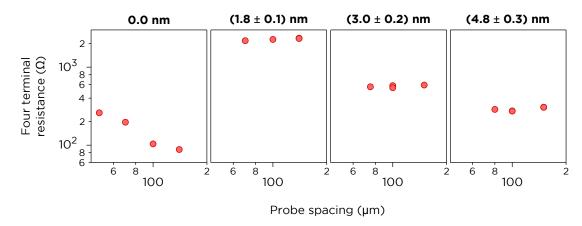

|   |     | 3.3.3  | Probe spacing dependent four-terminal measurements                          | 85  |

|   | 3.4 | Is con | duction really through the $\delta$ -layer alone?                           | 87  |

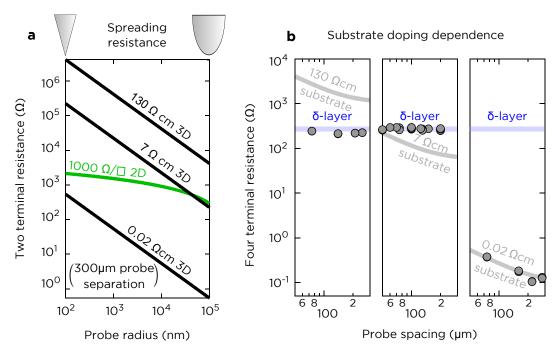

|   |     | 3.4.1  | Two-terminal measurements                                                   | 87  |

|   |     | 3.4.2  | Other 2-dimensional aspects of the sample                                   | 89  |

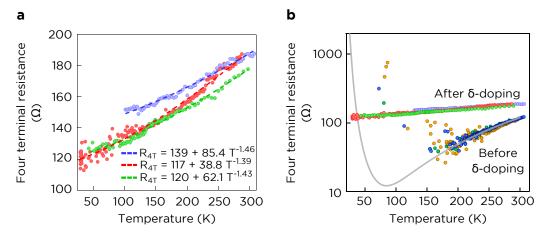

|   |     | 3.4.3  | Temperature dependence of resistivity                                       | 92  |

|   |     | 3.4.4  | What if conduction is through the $\delta$ -layer and the substrate in par- |     |

|   |     |        | allel?                                                                      | 94  |

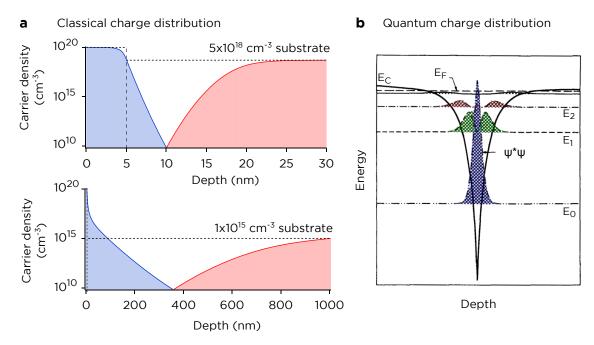

|   | 3.5 | Why o  | do we only observe conduction through the $\delta$ -layer?                  | 96  |

|   | 3.6 | Concl  | usions                                                                      | 99  |

| 4 | The |        | vity of near-surface Si:P $\delta$ -layers                                  | 101 |

|   | 4.1 | Introd | luction                                                                     | 103 |

|   |     | 4.1.1  | Why shallow doping?                                                         | 103 |

|   |     | 4.1.2  | A definition of terms                                                       | 104 |

|   |     | 4.1.3  | How is shallow doping achieved?                                             | 104 |

|   |     | 4.1.4  | How is shallow doping characterized?                                        | 105 |

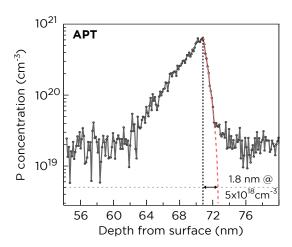

|   | 4.2 | Thern  | nal redistribution processes: how ' $\delta$ ' is a $\delta$ -layer?        | 108 |

|   | 4.3 | Depth  | dependent four-probe measurements of Si:P $\delta$ -layers                  | 112 |

|   |     | 4.3.1  | The ultimate ultra-shallow junction                                         | 112 |

|   |     | 4.3.2  | Depth dependence of the $\delta$ -doping layer resistivity                  | 113 |

|   |     | 4.3.3  | Depth dependence in context                                                 | 117 |

|   |     | 4.3.4  | How <i>electrically</i> wide is a delta layer?                              | 118 |

|   | 4.4 | Buildi | ng a model for the depth dependent conductivity                             | 121 |

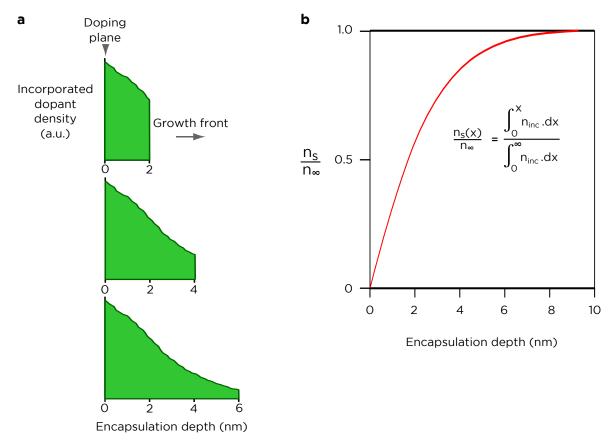

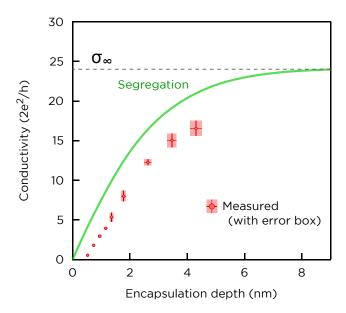

|   |     | 4.4.1  | A preliminary model: the role of segregation                                | 122 |

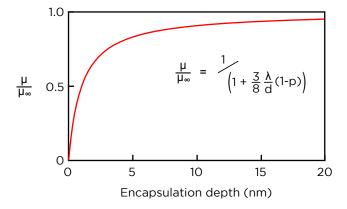

|   |     | 4.4.2  | An improved model: the role of surface scattering                           | 124 |

|   |     | 4.4.3  | The minimum observed conductance                                            | 127 |

|   |     | 4.4.4  | Avenues for further refinement                                              | 128 |

|   | 4.5 | Optin  | nizing the resistivity of shallow $\delta$ -layers                          | 130 |

|   |     | 4.5.1  | The chemistry of double dosing                                              | 130 |

|   |     | 4.5.2  | Depth dependence measurements                                               | 132 |

|   | 4.6 | Concl  | usions and outlook                                                          | 132 |

| 5 | Nan | oprobi | ng patterned Si:P dopant structures                                         | 135 |

|   | 5.1 | Introd | luction                                                                     | 137 |

|   |     | 5.1.1  | Why measure patterned structures?                                           | 137 |

|   |     | 5.1.2  | The problem of seeing what you're contacting                                | 138 |

#### Contents

|    |                                          | 5.1.3                            | The problem of placing the probes                        | 139 |  |

|----|------------------------------------------|----------------------------------|----------------------------------------------------------|-----|--|

|    | 5.2                                      | 5.2 Coarsely isolated structures |                                                          |     |  |

|    |                                          | 5.2.1                            | Experimental method                                      | 145 |  |

|    |                                          | 5.2.2                            | Measurement results                                      | 145 |  |

|    | 5.3                                      | Lithog                           | raphically patterned features                            | 147 |  |

|    |                                          | 5.3.1                            | Single probe measurements                                | 150 |  |

|    |                                          | 5.3.2                            | Multi-probe measurements                                 | 156 |  |

|    | 5.4                                      | Conclu                           | asions and outlook                                       | 159 |  |

| 6  | Con                                      | clusion                          | 6                                                        | 161 |  |

| U  | Con                                      | Clusion                          | 5                                                        | 101 |  |

| A  | App                                      | endix A                          | A: Deriving correction factors for 4-probe measurements  | 167 |  |

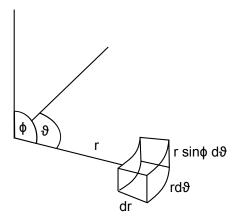

|    | A.1                                      | Potent                           | ial distribution from a single tip                       | 167 |  |

|    | A.2                                      | $\Phi$ on a                      | 3-dimensional substrate                                  | 168 |  |

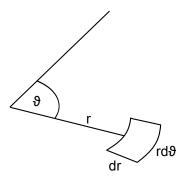

|    | A.3 $\Phi$ on a 2-dimensional substrate  |                                  |                                                          |     |  |

|    | A.4 Resistance $\rightarrow$ Resistivity |                                  |                                                          |     |  |

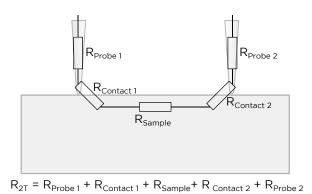

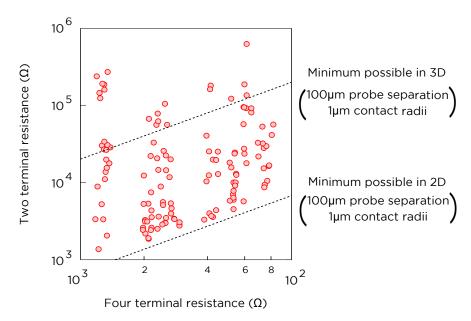

|    | A.5 Two-terminal resistances             |                                  |                                                          |     |  |

| В  | B Appendix B: Code Listings 1            |                                  |                                                          |     |  |

|    | B.1                                      | Comp                             | uting the propagated error from probe positioning errors | 175 |  |

|    | B.2                                      | Simula                           | ating carrier density freezeout                          | 178 |  |

|    | B.3                                      |                                  | ating the diffusion of a $\delta$ -doping profile        | 181 |  |

|    |                                          |                                  |                                                          |     |  |

| Re | efere                                    | nces                             |                                                          | 198 |  |

|    |                                          |                                  |                                                          |     |  |

## Chapter 1

### Introduction

In 1992 the cutting edge of personal computer processors was the Intel 486, which was built from an impressive 1.2 *million* transistors. Twenty years later, this introduction is being written with the help of an Intel Core i7 processor, which is built from 1.2 *billion* transistors. Advancement this rapid in any other field of engineering would be astonishing, but for computer processors it is simply 'business as usual'. The aggressive increases in transistor density have been consistent since the inception of integrated circuits in the 1960's, and as a result have become a defining characteristic of the modern semiconductor industry. The majority of people alive today have never known a time when computers did not become cheaper and faster every year.

And yet such a time will certainly come within our lifetimes, if not for engineering reasons then simply due to the discreteness of matter. Manufacturing is already at the '22 nm' node today in 2012; iterations through the '16 nm' and '11 nm' nodes are expected by 2018 but it is not clear that conventional planar transistor architectures are viable beyond this point<sup>1</sup>. At such length scales, transistor characteristics are strongly influenced by unavoidable effects such as quantum mechanical tunneling and the stray placement of individual atoms<sup>2</sup>. As a consequence, research efforts in computing technology today are divided between developing new tools and processes to extend planar CMOS scaling as far as possible ('More Moore') while also planning for radical new materials and information processing technologies ('More than Moore'). 'More Moore' involves advances in areas such as lithography, precision ultra-shallow doping and high-permittivity dielectric materials. 'More than Moore' is a broader topic; from a materials perspective it involves planning for the integration of new materials such as high-mobility or optically active III-V semiconductors, germanium and graphene. However it also encompasses entirely new approaches to information processing such as quantum<sup>3;4</sup>, spin<sup>5</sup> or DNA<sup>6</sup> computing, often even going beyond Boolean logic. It is an exciting time to be involved in research.

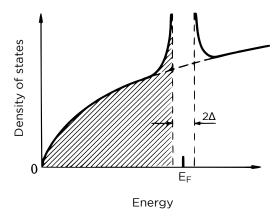

An area critical to several of these research areas is the planar doping of semiconductors. The work in this thesis is based on the precision phosphorus in silicon doping scheme developed at UNSW by the Simmons group<sup>7</sup>. By exposing phosphine gas to a

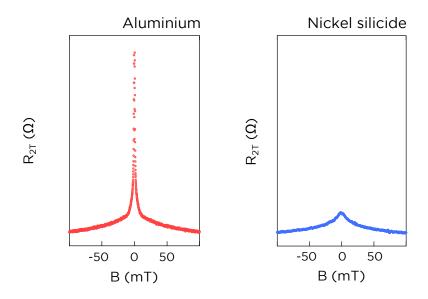

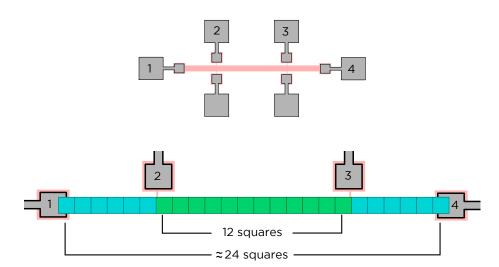

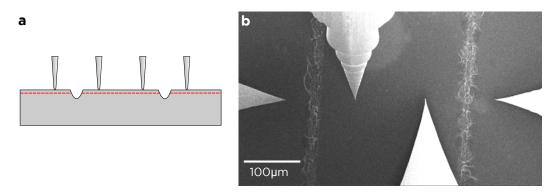

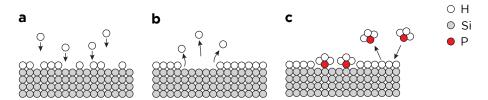

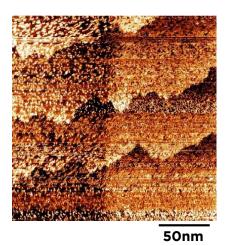

clean, reactive silicon 2×1 surface in ultra-high vacuum (UHV) and heating the surface to 350°C, a self-limiting quarter monolayer of phosphorus is incorporated into the surface layer of the silicon crystal lattice. Low temperature epitaxial encapsulation of the dopants completes their crystalline environment and allows precise control over the depth of the doping plane from the silicon-vacuum interface. This doping process can be extended to include lithography by hydrogen passivating the reacting starting surface and selectively desorbing hydrogen atoms with a scanning tunneling microscope. The phosphine precursor then only adsorbs to depassivated areas of the surface, which can be created with atomic precision. Removing such samples from the UHV environment to add ex situ Ohmic contacts<sup>8</sup> enables low-temperature magnetotransport measurements of the nanoscale dopant 'devices'. To date this technology has been employed for the study of a variety of quantum electronic devices, including tunnel gaps<sup>8</sup>, nanowires<sup>9</sup>, Aharonov-Bohm rings <sup>10</sup> and perhaps most importantly quantum dots, which due to the strengths of the STM-lithography approach have been progressively and successfully scaled down to the limit of a single phosphorus donor <sup>11;12;13</sup>. The latter constitutes a key milestone in the realization of a scalable solid state quantum computer <sup>14</sup>.

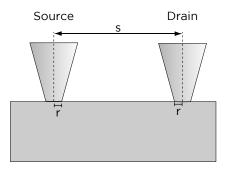

For the furtherance of planar transistor scaling, part of this thesis is dedicated to investigating the application of the Si:P  $\delta$ -doping technique for ultra-shallow doping profiles in silicon. Such 'ultra-shallow junctions' are typically employed as part of the source and drain contacts in conventional planar transistor architectures, where they are crucial for the control of the 'short channel effects', negative operating characteristics which emerge as a consequence of aggressive downscaling. The Si:P  $\delta$ -doping method, with its high doping densities ( $\approx 2 \times 10^{14} \text{cm}^{-2}$ ), abrupt impurity profiles and atomic-resolution control of the encapsulation depth is ideal for investigating the limits of ultra-shallow junction scaling. We couple this with a novel *in situ* UHV four-point-probe STM system in order to electrically characterize these shallow doping layers while maintaining full control over the surface condition, allowing us to truly explore the physical limit of shallow doping technology.

Towards the development of novel 'post-CMOS' computing technology we develop an improved processing sequence for the creation of nickel silicide Ohmic contacts to Si:P dopant devices, solving problems related to reliability and low-temperature magnetotransport artifacts. We also lay the foundations for the four-probe *in situ* electrical characterization of STM-patterned dopant structures, building towards the long-term capability of measuring surface related structures such as molecules <sup>15</sup>, nanowire interconnects <sup>9</sup> and even dangling bond logic gates <sup>16</sup>.

#### Chapter 1. Introduction

#### Thesis outline

In **chapter 2** we develop an optimized Ohmic contacting scheme for STM-patterned buried dopant devices in silicon. Existing contacting methods for these devices use aluminium, which suffers reliability issues as well as superconductivity artifacts at the low temperatures used for quantum transport measurements. We show that many desirable properties of nickel silicide make it a leading candidate for a replacement, and proceed to develop a low temperature processing sequence for creating nickel silicide contacts to STM patterned devices. We perform extensive low-temperature comparative magnetotransport measurements to verify the improvement over aluminium contacts.

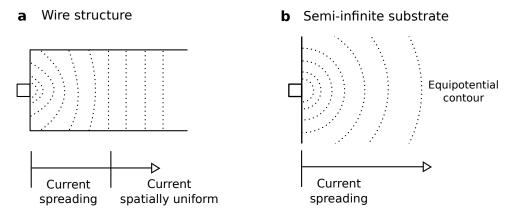

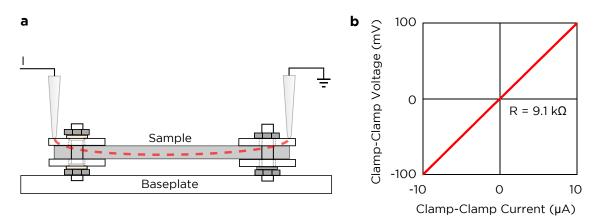

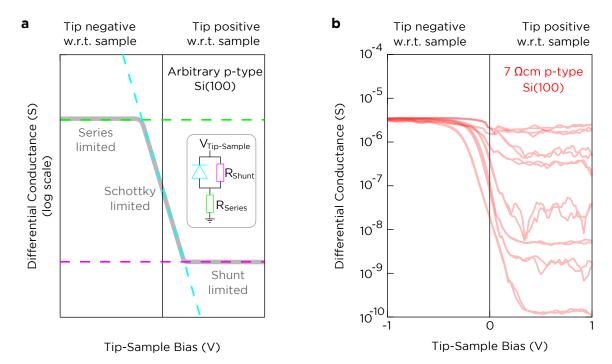

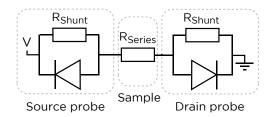

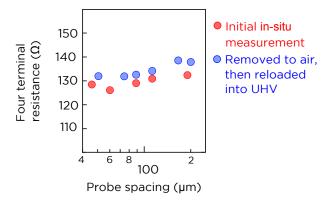

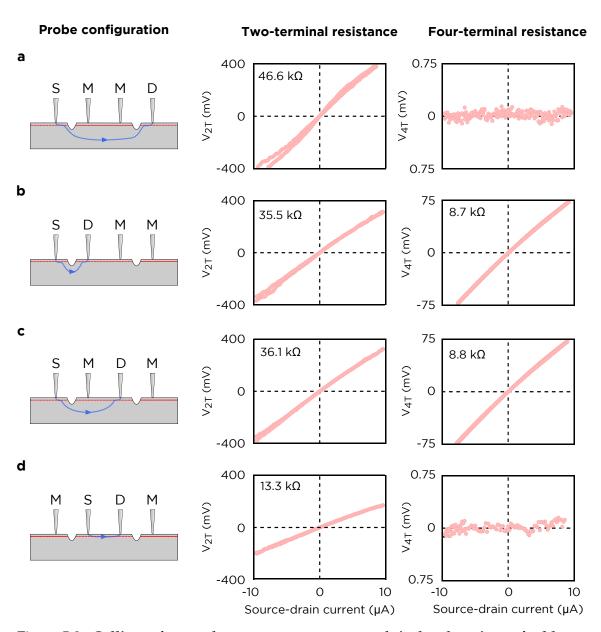

Chapter 3 is concerned with the application of a novel characterization technique - the in situ nanoscale four-point probe - to measuring the room temperature resistivity of near surface Si:P  $\delta$ -doping profiles in silicon. We develop a comprehensive understanding of the nanoscale four-probe tool and how it can be applied to unambiguously determine the resistivity of both bulk and  $\delta$ -doped silicon samples. In particular, we show conclusively that despite the use of conductive substrates, electrical measurements with this tool can be used to measure the resistance of the  $\delta$ -layer only, due to spreading resistance effects.

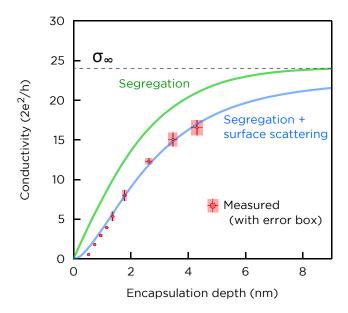

In **chapter 4** we apply our newly developed knowledge to study the *in situ* resistivity of Si:P  $\delta$ -layers as a function of the vertical distance of the doping profile from the silicon interface. Such layers can be considered 'ultimate' versions of the ultra-shallow junctions critical to future transistor scaling. Measuring the resistivity for depths ranging from 20 nm all the way down to 0 nm with ångstrom resolution, we report values of sheet resistance which surpass all currently projected ITRS requirements (out to 2015). We provide a physical model for the observed depth dependent conductivity based on segregation and surface scattering, which closely matches experimental data.

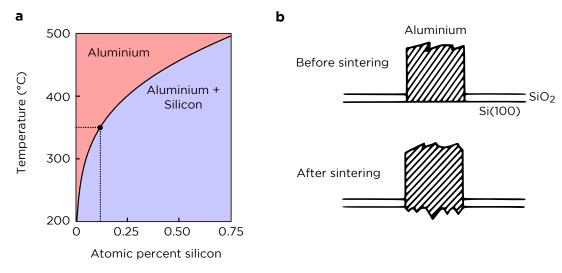

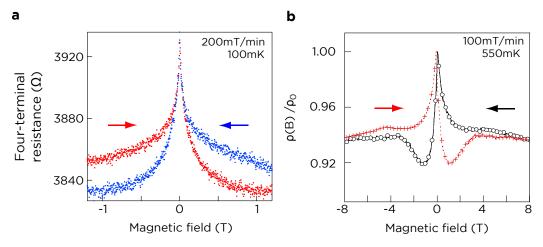

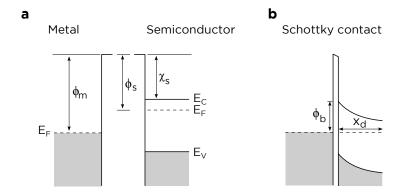

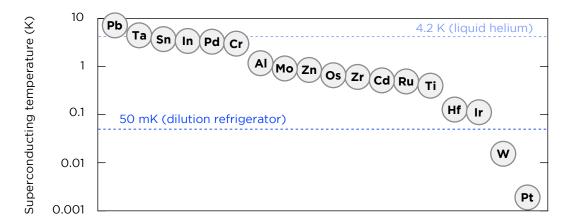

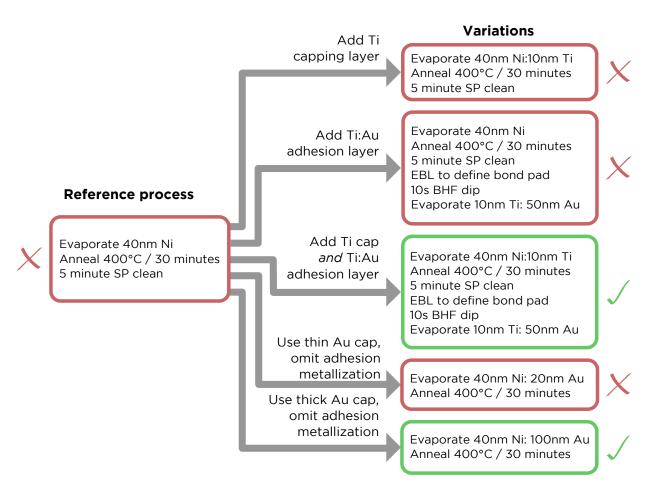

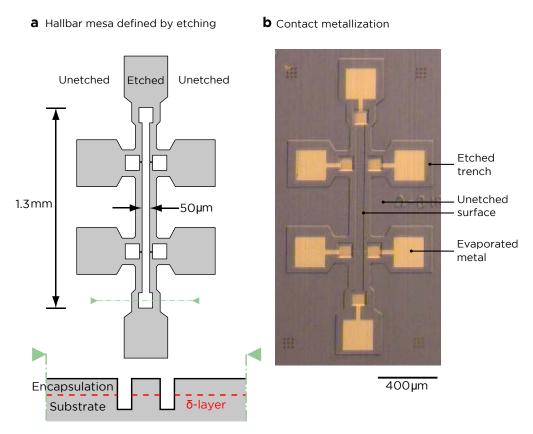

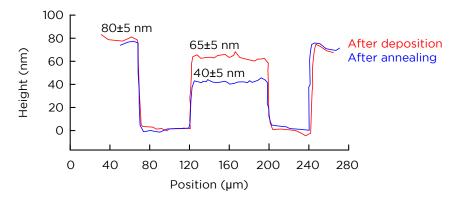

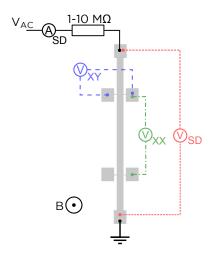

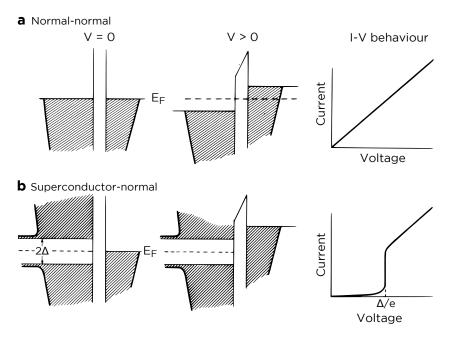

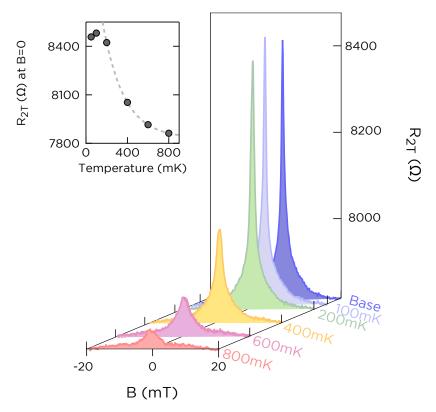

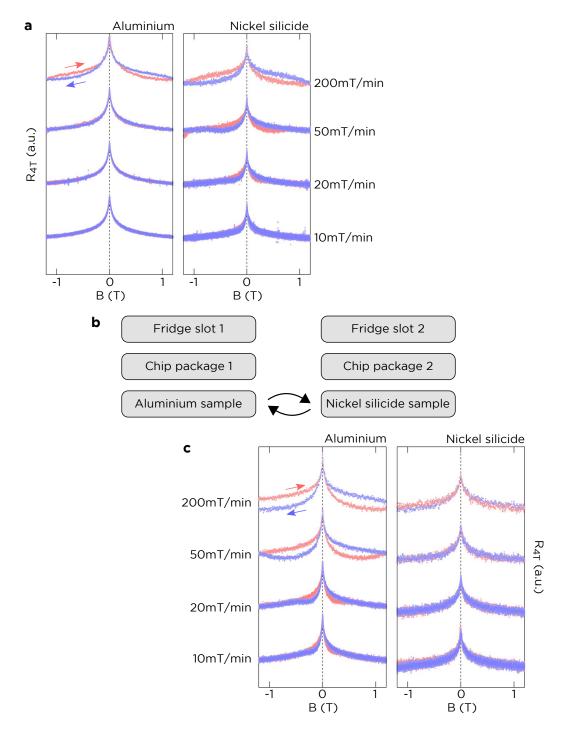

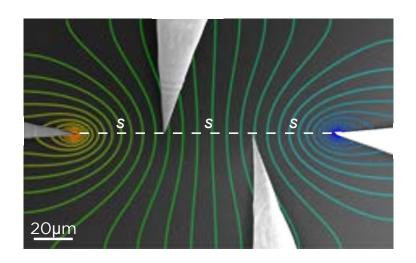

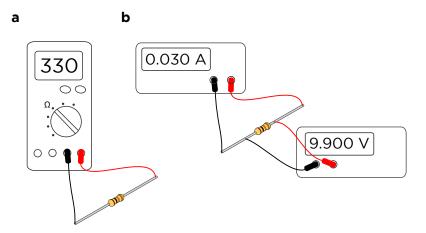

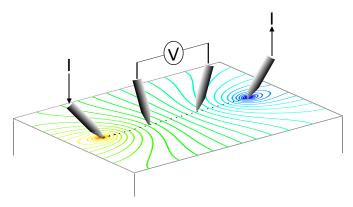

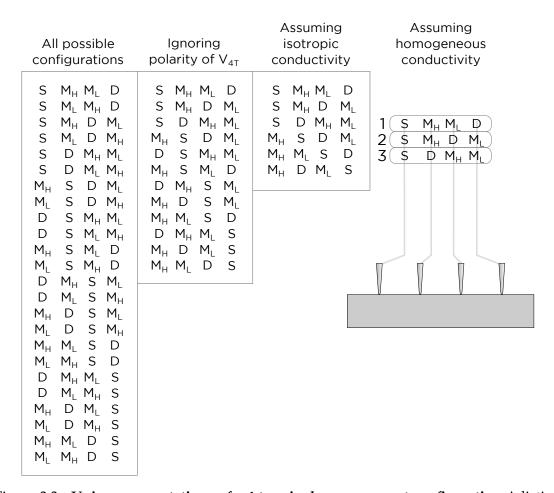

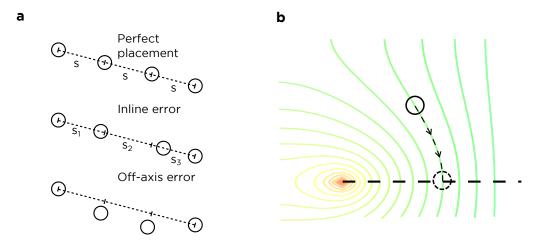

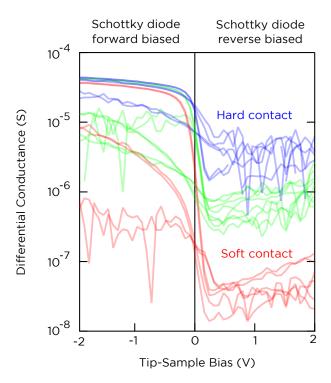

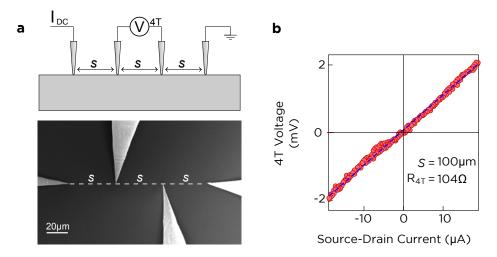

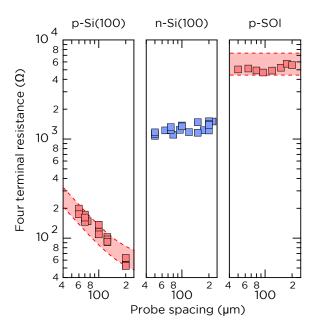

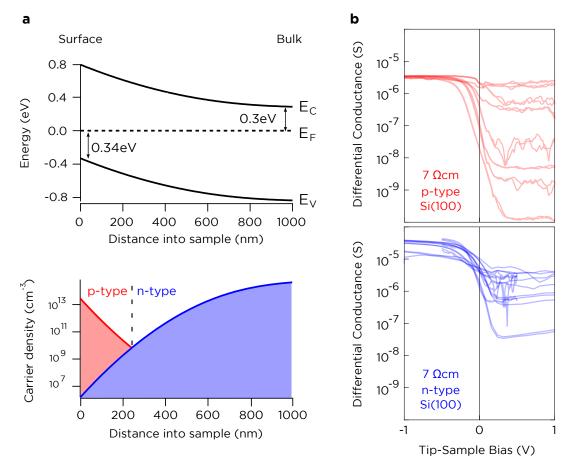

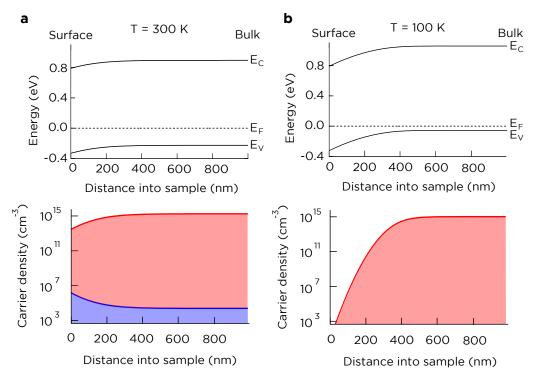

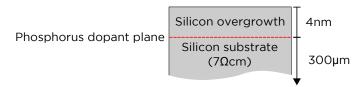

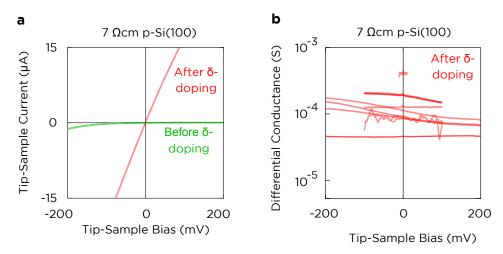

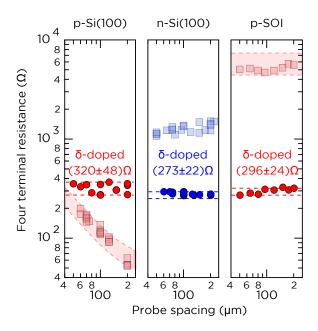

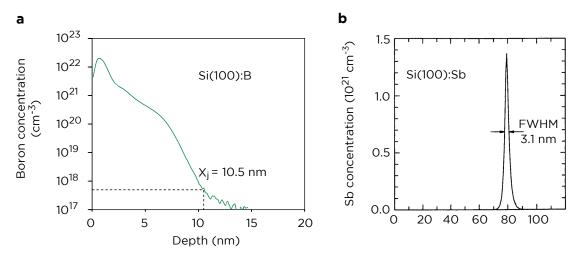

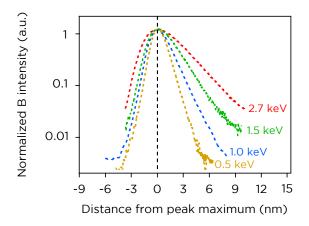

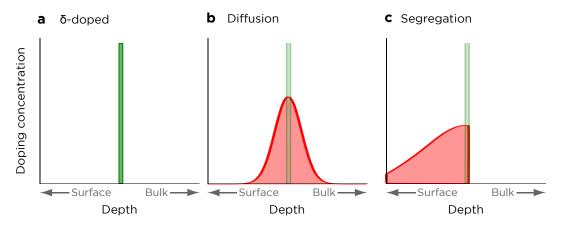

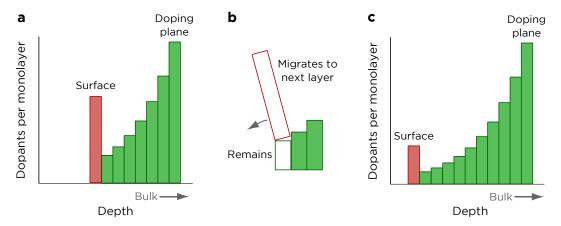

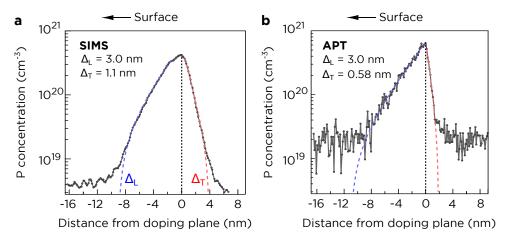

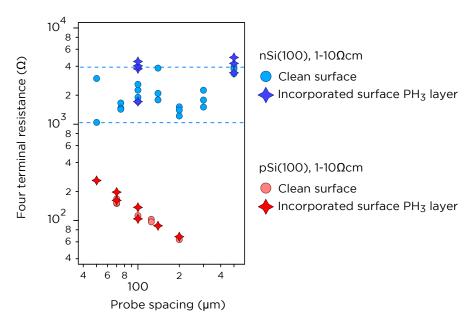

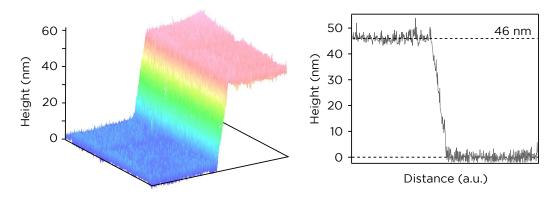

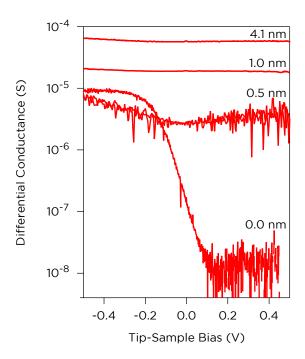

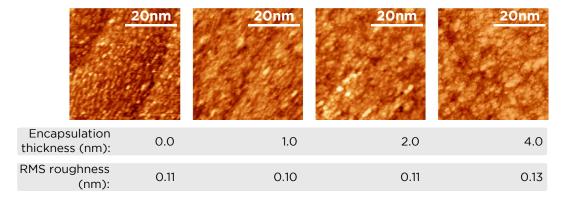

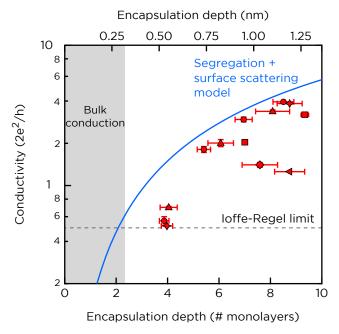

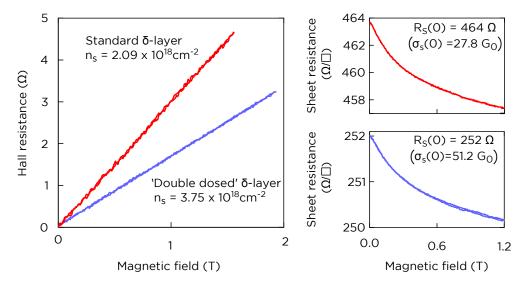

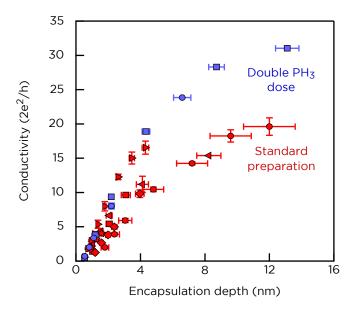

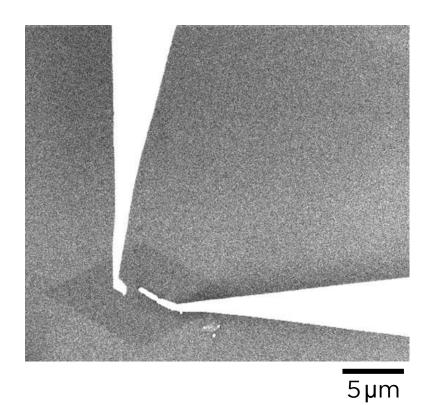

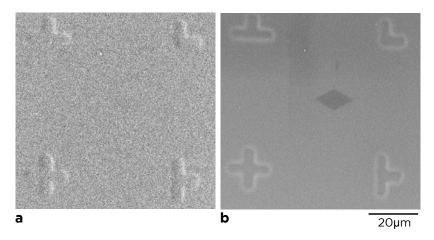

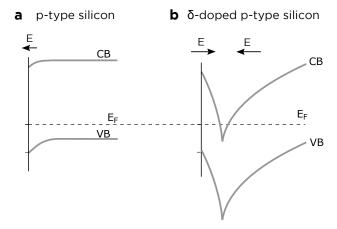

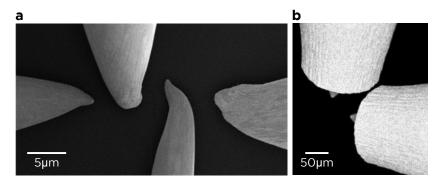

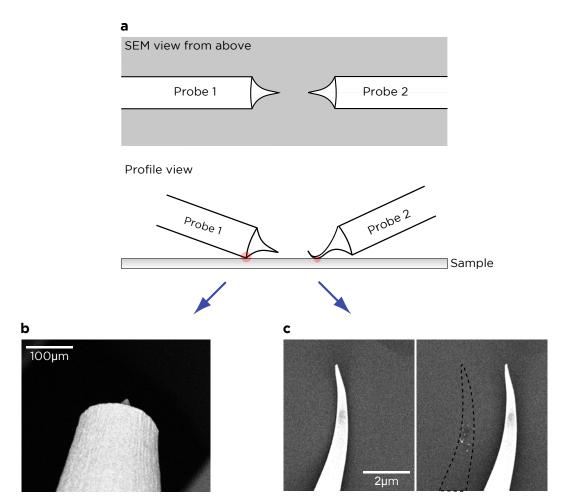

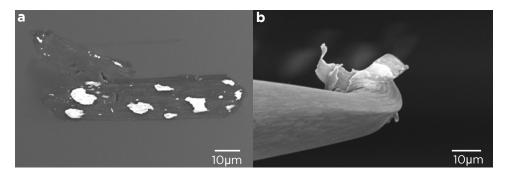

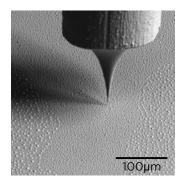

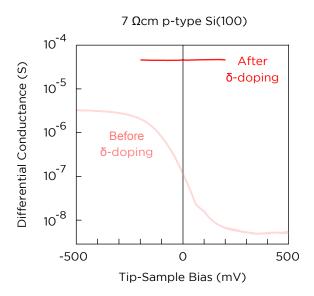

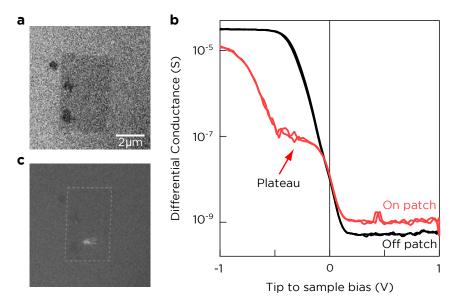

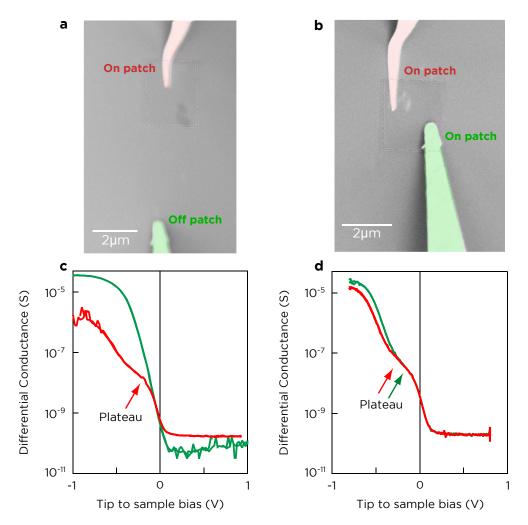

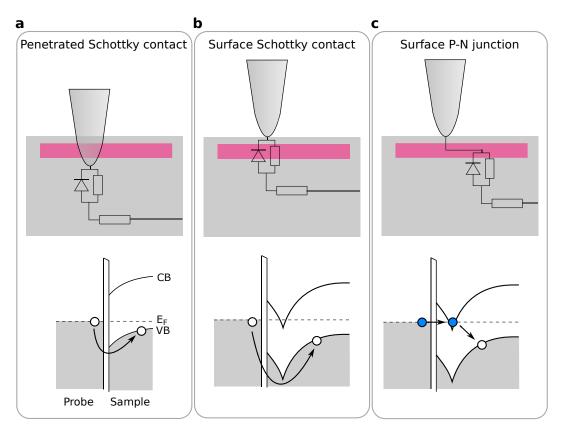

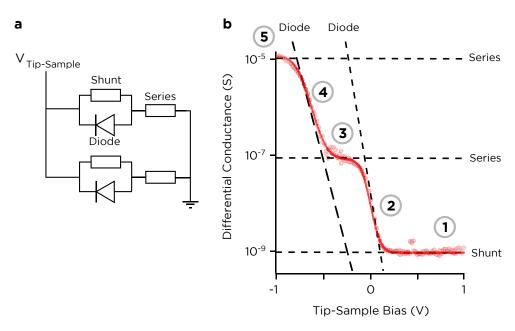

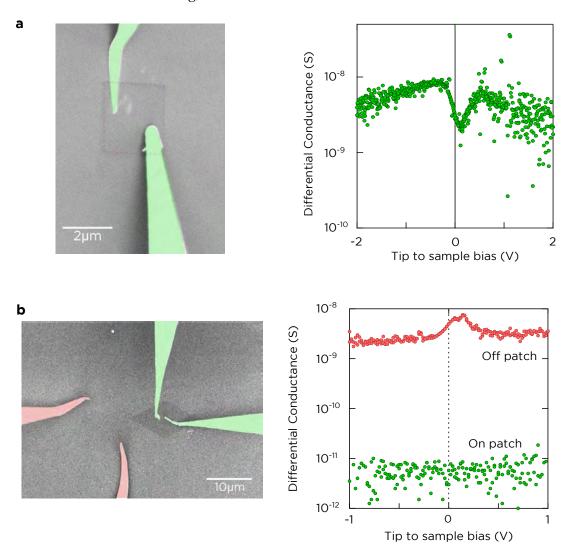

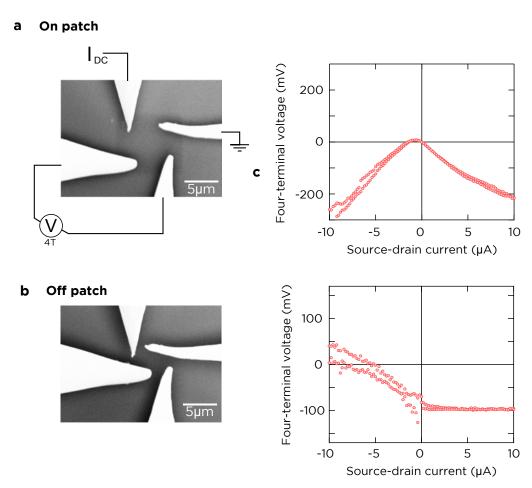

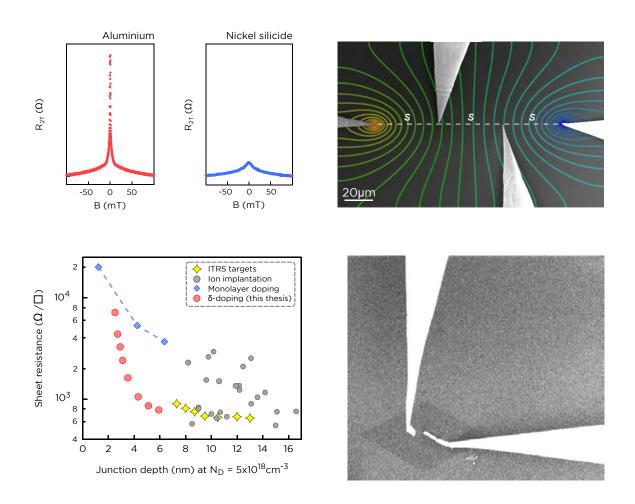

Chapter 5 aims to further extend the combination of *in situ* four-probe and near-surface Si:P  $\delta$ -doping by electrically characterizing lithographically defined dopant regions. We provide important verification that current passed through a dopant pattern at room temperature remains confined to that pattern and does not spread through the underlying substrate. We also demonstrate that probe-to-sample current-voltage measurements display a unique and unambiguous conductance feature when placed over a dopant patch, and that this can be used to verify the accuracy of probe positioning. Building on these findings, we show preliminary measurements of micrometer-scale dopant patterns.